| LTR | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    | DATE (YR-MO-DA) | APPROVED          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|

| A   | Add case outline U. Add note 2/ to sheet 2. Add note 5/ to table IA. Add note 6/ to t <sub>WHWL</sub> . Make corrections to notes on sheets 11 and 13. Add note 3 to figure 3. Add note 2 to figure 5, Read Cycle. Add note 6 to figure 5, Write Cycle. Make correction to note 5 of figure 6. Add vendor CAGE 34168 as source of supply for case outline U. Editorial corrections throughout. | 97-06-12        | Raymond Monnin    |

| В   | Corrections to sheet 16, Figure 2, Terminal Connections glg                                                                                                                                                                                                                                                                                                                                    | 01-01-05        | Raymond Monnin    |

| С   | Change CAGE code to correct CAGE of 67268. Update boilerplate. Editorial changes throughout gap                                                                                                                                                                                                                                                                                                | 02-04-08        | Raymond Monnin    |

| D   | Updated paragraph 4.4.4.2d; added paragraph 4.4.4.2e, and added paragraph 6.6.3. Corrected the S dimension for the Y package and corrected the polarity of the capacitor pads for package Z. Updated boilerplate as part of 5 year review ksr                                                                                                                                                  | 09-05-18        | Joseph Rodenbeck  |

| E   | Updated body of drawing to reflect current requirements. Added appendix B for die glg                                                                                                                                                                                                                                                                                                          | 11-10-18        | Charles F. Saffle |

| F   | Updated Figure 4 to reflect vendor's current modeling and testing methods.  Removed class M references glg                                                                                                                                                                                                                                                                                     | 13-12-20        | Charles F. Saffle |

| G   | Add supply voltage ramp time to section 1.4. Updated table IB to reflect vendor's current modeling and testing methods glg                                                                                                                                                                                                                                                                     | 14-04-10        | Charles F. Saffle |

| Н   | Correct Table IA timing parameter Chip enable/select access time (tEHQV/tSLQV) by moving from minimum to maximum column glg                                                                                                                                                                                                                                                                    | 14-08-08        | Charles F. Saffle |

| J   | Updated drawing to reflect current MIL-PRF-38535 requirements. Correct 1.3 for Supply voltage range and Maximum power dissipation. Update 2.2. Update 4.2.2 to 4.2.1. Correct 4.4.4.2 for time Ilb                                                                                                                                                                                             | 14-11-24        | Charles F. Saffle |

| K   | Update to current MIL-PRF-38535 requirements. – IIb                                                                                                                                                                                                                                                                                                                                            | 20-11-09        | James Eschmeyer   |

| REV                                               |         |        |                                 |                                   |         |    |       |                                                                                                                 |                                                                      |      |       |      |     |    |    |     |    |    |    |    |

|---------------------------------------------------|---------|--------|---------------------------------|-----------------------------------|---------|----|-------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|-------|------|-----|----|----|-----|----|----|----|----|

| SHEET                                             |         |        |                                 |                                   |         |    |       |                                                                                                                 |                                                                      |      |       |      |     |    |    |     |    |    |    |    |

| REV                                               | K       | K      | K                               | K                                 | K       | K  | K     | K                                                                                                               | K                                                                    | K    | K     | K    | K   | K  | K  | K   | K  | K  | K  | K  |

| SHEET                                             | 15      | 16     | 17                              | 18                                | 19      | 20 | 21    | 22                                                                                                              | 23                                                                   | 24   | 25    | 26   | 27  | 28 | 29 | 30  | 31 | 32 | 33 | 34 |

| REV STATUS                                        |         |        |                                 | REV                               | /       |    | K     | K                                                                                                               | K                                                                    | K    | K     | K    | K   | K  | K  | K   | K  | K  | K  | K  |

| OF SHEETS                                         |         |        |                                 | SHE                               | ET      |    | 1     | 2                                                                                                               | 3                                                                    | 4    | 5     | 6    | 7   | 8  | 9  | 10  | 11 | 12 | 13 | 14 |

| PMIC N/A                                          |         |        |                                 | PREPARED BY Jeff Bowling          |         |    |       | DLA LAND AND MARITIME                                                                                           |                                                                      |      |       |      |     |    |    |     |    |    |    |    |

| STAN<br>MICRO                                     | CIRC    | CUIT   |                                 | CHECKED BY<br>Jeff Bowling        |         |    |       | COLUMBUS, OHIO 43218-3990 <a href="https://www.dla.mil/LandandMaritime">https://www.dla.mil/LandandMaritime</a> |                                                                      |      |       |      |     |    |    |     |    |    |    |    |

| DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL |         |        | APPROVED BY<br>Michael. A. Frye |                                   |         |    |       |                                                                                                                 |                                                                      |      |       |      | DIG |    |    | v o |    |    |    |    |

| DEPAR<br>AND AGEN<br>DEPARTMEN                    | ICIES ( | OF THE |                                 | DRAWING APPROVAL DATE<br>96-11-26 |         |    |       |                                                                                                                 | RADIATION-HARDENED, CMOS/SOI, 32K X 8 STATIC RAM, MONOLITHIC SILICON |      |       |      |     |    |    |     |    |    |    |    |

| AMSC N/A REVISION LEVEL                           |         |        |                                 | · · ·                             | ZE<br>A |    | GE CC |                                                                                                                 |                                                                      | 5    | 5962- | 9584 | 5   |    |    |     |    |    |    |    |

|                                                   |         |        |                                 |                                   |         | (  | SHEET |                                                                                                                 | 1                                                                    | OF 3 | 34    |      |     |    |    |     |    |    |    |    |

DSCC FORM 2233 APR 97

# 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device class Q) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

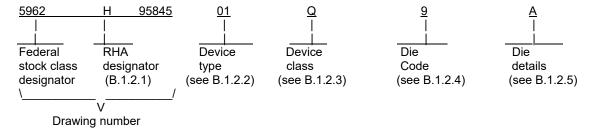

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device types</u>. The device types identify the circuit function as follows:

| Device type | Generic number | Circuit function      | Input/output levels | Chip enable 1/ | Access time |

|-------------|----------------|-----------------------|---------------------|----------------|-------------|

| 01          | HX6256         | 32K X 8 CMOS/SOI SRAM | CMOS                | Dual           | 25 ns       |

| 02          | HX6256         | 32K X 8 CMOS/SOI SRAM | TTL                 | Dual           | 25 ns       |

| 03          | HX6356         | 32K X 8 CMOS/SOI SRAM | CMOS                | Dual           | 25 ns       |

| 04          | HX6356         | 32K X 8 CMOS/SOI SRAM | TTL                 | Dual           | 25 ns       |

| 05          | HX6256         | 32K X 8 CMOS/SOI SRAM | CMOS                | Dual           | 20 ns       |

| 06          | HX6256         | 32K X 8 CMOS/SOI SRAM | TTL                 | Dual           | 20 ns       |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

Q or V

Certification and qualification to MIL-PRF-38535

1.2.4 Case outlines. The case outlines are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style |

|----------------|------------------------|------------------|---------------|

| X              | GDIP1-T28 or CDIP2-T28 | 28               | Dual-in-line  |

| Υ              | See figure 1           | 28               | Flat pack     |

| Z              | See figure 1           | 36               | Flat pack     |

| U              | See figure 1           | 36               | Flat pack     |

1.2.5 Lead finish. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V.

1/ Any device type ordered in case outlines X or Y is single chip enable.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 2    |

# 1.3 Absolute maximum ratings. 2/ 3/

| Supply voltage range (V <sub>CC</sub> )                  | -0.5 V dc to +7 V dc                    |

|----------------------------------------------------------|-----------------------------------------|

| DC input voltage range (V <sub>IN</sub> )                | -0.5 V dc to V <sub>CC</sub> + 0.5 V dc |

| DC output voltage range (Vout)                           | -0.5 V dc to V <sub>CC</sub> + 0.5 V dc |

| Storage temperature range                                | -65°C to +150°C                         |

| Lead temperature (soldering, 5 seconds)                  | +270°C                                  |

| Thermal resistance, junction-to-case (θ <sub>JC</sub> ): |                                         |

| Case X                                                   | See MIL-STD-1835                        |

| Cases Y, Z, and U                                        | 2.0°C/W                                 |

| Output voltage applied to high Z state                   | -0.5 V dc to V <sub>CC</sub> + 0.5 V dc |

| Maximum power dissipation (P <sub>D</sub> )              | 2.5 W                                   |

| Maximum junction temperature (T <sub>J</sub> )           | +175°C                                  |

|                                                          |                                         |

# 1.4 Recommended operating conditions.

| Supply voltage range (V <sub>CC</sub> )            | 4.5 V dc (min) to 5.5 V dc (max)                      |

|----------------------------------------------------|-------------------------------------------------------|

| Supply voltage (Vss)                               | 0.0 V dc                                              |

| Supply voltage ramp time                           | 50 ms maximum                                         |

| High level input voltage range (V <sub>IH</sub> ): |                                                       |

| Device type 01, 03, 05 (CMOS levels)               | $0.7 \text{ x V}_{CC}$ to $V_{CC} + 0.3 \text{ V dc}$ |

| Device type 02, 04, 06 (TTL levels)                | $2.2 \text{ V}$ dc to $V_{CC}$ + $0.3 \text{ V}$ dc   |

| Low level input voltage range (V <sub>IL</sub> ):  |                                                       |

| Device type 01, 03, 05 (CMOS levels)               | -0.3 V dc to 0.3 x V <sub>CC</sub>                    |

| Device type 02, 04, 06 (TTL levels)                | -0.3 V dc to 0.8 V dc                                 |

| Case operating temperature range (T <sub>C</sub> ) | -55°C to +125°C                                       |

|                                                    |                                                       |

#### 1.5 Radiation features.

| Maximum total dose available (dose rate = 50 – 300 rads(Si)/s)<br>Single event phenomenon (SEP) (see 4.4.4.3): | 1 Mrads(Si)                            |    |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------|----|

| Heavy ion test:                                                                                                |                                        |    |

| No SEL at an effective LET                                                                                     | ≤ 120 MeV-cm <sup>2</sup> /mg          |    |

| SEU error rate                                                                                                 | 1.0 x 10 <sup>-10</sup> upsets/bit-day | 4/ |

#### 1.6 Digital logic testing for device classes Q and V.

| Fault coverage measurement of manufacturing |             |

|---------------------------------------------|-------------|

| logic tests (MIL-STD-883, method 5012)      | 100 percent |

| STANDARD MICROCIRCUIT DRAWING                      | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 3    |

Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

<sup>3/</sup> All voltages referenced to V<sub>SS</sub> (V<sub>SS</sub> = ground), unless otherwise specified.

Based on CREME96 results for a geosynchronous orbit during solar minimum non-flare conditions behind 100mil Aluminum shield. Weibull parameters are available from the vendor to calculate projected upset rates for other orbits/environments (such as Adams 90% worst case) and using different upset rate calculating programs (such as Space Radiation 5.0).

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

#### DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at https://guicksearch.dla.mil/.)

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents are the issues of the documents cited in the solicitation.

#### ASTM INTERNATIONAL (ASTM)

ASTM Standard F1192 - Standard Guide for the Measurement of Single Event Phenomena from Heavy Ion Irradiation of Semiconductor Devices.

(Copies of these documents are available online at https://www.astm.org.)

JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JESD 78 - IC Latch-Up Test.

(Copies of these documents are available online at <a href="https://www.jedec.org">https://www.jedec.org</a>.)

2.3 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

| STANDARD                  |  |  |  |  |

|---------------------------|--|--|--|--|

| MICROCIRCUIT DRAWING      |  |  |  |  |

| DLA LAND AND MARITIME     |  |  |  |  |

| COLUMBUS, OHIO 43218-3990 |  |  |  |  |

| SIZE<br><b>A</b> |                     | 5962-95845 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>K | SHEET 4    |

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 as specified herein, or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 3.1.1 Microcircuit die. For the requirements of microcircuit die, see appendix B to this document.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V.

- 3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.4 herein and figure 1.

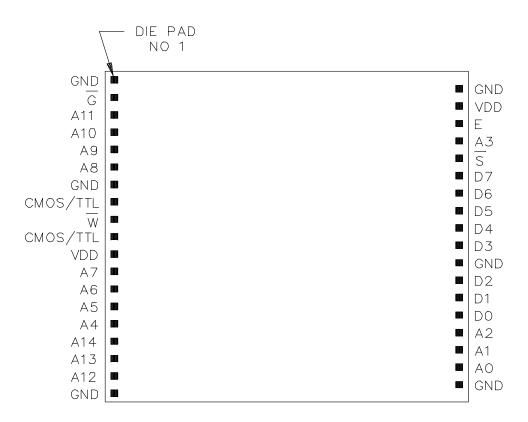

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

- 3.2.3 Truth table. The truth table shall be as specified on figure 3.

- 3.2.4 Output load circuit. The output load circuit shall be as specified on figure 4.

- 3.2.5 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 5.

- 3.2.6 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing and acquiring activity upon request.

- 3.2.7 <u>Functional tests</u>. Various functional tests used to test this device are contained in the appendix A. If the test patterns cannot be implemented due to test equipment limitations, alternate test patterns to accomplish the same results shall be allowed. For device classes Q and V alternate test patterns shall be under the control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the preparing or acquiring activity upon request.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table IA and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table IA.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535.

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). The certificate of compliance submitted to DLA Land and Maritime-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.2.8 <u>Die overcoat</u>. Polyimide and silicone coatings are allowable as an overcoat on the die for alpha particle protection only. Each coated microcircuit inspection lot (see inspection lot as defined in MIL-PRF-38535) shall be subjected to and pass the internal moisture content test at 5000 ppm (see method 1018 of MIL-STD-883). The TRB will ascertain the requirements as provided by MIL-PRF-38535 for classes Q and V. Samples may be pulled any time after seal.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 5    |

TABLE IA. <u>Electrical performance characteristics</u>.

| Test                        | Symbol          | Conditions<br>$-55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125^{\circ}\text{C}$<br>$4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V}$ |                                                                     | Group A<br>subgroups | Device<br>type    |            | nits       | Unit |

|-----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------|-------------------|------------|------------|------|

| High level output voltage   | Vон             | V <sub>CC</sub> =                                                                                                                                      | 4.5 V, I <sub>OH</sub> = -5 mA,<br>1.35 V, V <sub>IH</sub> = 3.15 V | 1, 2, 3              | 01, 03, 05        | Min<br>4.2 | Max        | V    |

|                             |                 | V <sub>CC</sub> =                                                                                                                                      | 4.5 V, I <sub>OH</sub> = -4 mA,<br>0.8 V, V <sub>IH</sub> = 2.2 V   |                      | 02, 04, 06        | 4.2        |            |      |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   | <u>2</u> / |            |      |

| Low level output voltage    | VoL             |                                                                                                                                                        | 4.5 V, I <sub>OL</sub> = 10 mA,<br>1.35 V, V <sub>IH</sub> = 3.15 V | 1, 2, 3              | 01, 03, 05        | _          | 0.4        | V    |

|                             |                 |                                                                                                                                                        | 4.5 V, I <sub>OL</sub> = 8 mA,<br>0.8 V, V <sub>IH</sub> = 2.2 V    |                      | 02, 04, 06        |            | 0.4        |      |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   |            | <u>2</u> / |      |

| Input leakage current       | lilk            |                                                                                                                                                        | 0.0 V to 5.5 V, all other<br>at 0.0 V, V <sub>CC</sub> = 5.5 V      | 1, 2, 3              | All               | -5         | 5          | μΑ   |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   | <u>2</u> / | <u>2</u> / |      |

| Output leakage current      | Іоцк            |                                                                                                                                                        | = 0.0 V to 5.5 V, all other<br>at 0.0 V, V <sub>CC</sub> = 5.5 V    | 1, 2, 3              | All               | -10        | 10         | μA   |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   | <u>2</u> / | <u>2</u> / |      |

| Data retention voltage      | V <sub>DR</sub> | V <sub>CC</sub> =                                                                                                                                      | 2.5 V                                                               | 1, 2, 3              | All               | 2.5        |            | μΑ   |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   | <u>2</u> / |            |      |

| Operating supply current    | Icc1            | $\overline{S} = G$                                                                                                                                     | 5.5 V, no output loading ND, E = $V_{CC}$ $f_{MAX}$ $3/$            | 1, 2, 3              | All               |            | 160        | mA   |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   |            | <u>2</u> / |      |

| Supply current (deselected) | Icc2            | $\overline{S} = V_0$                                                                                                                                   | 5.5 V, $f = f_{MAX} 3/$<br>cc, $E = GND 4/$                         | 1, 2, 3              | All               |            | 1.5        | mA   |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   |            | <u>2</u> / |      |

| Supply current (standby)    | Іссз            |                                                                                                                                                        | 5.5 V, f = 0 Mhz,<br>cc, E = GND                                    | 1, 2, 3              | All               |            | 1.5        | mA   |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   |            | <u>2</u> / |      |

| Data retention current      | Icc4            | V <sub>CC</sub> =                                                                                                                                      | 2.5 V                                                               | 1, 2, 3              | 01, 02, 05,<br>06 |            | 500        | μΑ   |

|                             |                 | V <sub>CC</sub> =                                                                                                                                      | 3.0 V                                                               |                      | 03, 04            |            | 330        |      |

|                             |                 |                                                                                                                                                        | M, D, L, P, R, F, G, H                                              | 1 <u>1</u> /         |                   |            | <u>2</u> / |      |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 6    |

TABLE IA. <u>Electrical performance characteristics</u> – Continued.

| Test                          | Symbol            | $ Conditions \\ -55^{\circ}C \leq T_{C} \leq +125^{\circ}C \\ 4.5 \ V \leq V_{CC} \leq 5.5 \ V \\ unless \ otherwise \ specified $ | Group A<br>subgroups | Device<br>type | Lim        | nits<br>Max | Unit |

|-------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|------------|-------------|------|

| Input capacitance <u>5</u> /  | Cin               | V <sub>I</sub> = 5.0 V or 0.0 V, f = 1 MHz<br>T <sub>A</sub> = +25°C, see 4.4.1d                                                   | 4                    | All            |            | 7           | pF   |

| Output capacitance <u>5</u> / | Соит              | V <sub>O</sub> = 5.0 V or 0.0 V, f = 1 MHz<br>T <sub>A</sub> = +25°C, see 4.4.1d                                                   | 4                    | All            |            | 9           | pF   |

| Functional tests              |                   | See 4.4.1c                                                                                                                         | 7, 8A, 8B            | All            |            |             |      |

|                               |                   | M, D, L, P, R, F, G, H                                                                                                             | 7 <u>1</u> /         |                | <u>2</u> / |             |      |

| Read cycle time               | tavav             | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            | 25         |             | ns   |

|                               |                   | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                | <u>2</u> / |             |      |

| Address access time           | tavqv             | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            |            | 25          | ns   |

|                               |                   | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                |            | <u>2</u> /  |      |

| Chip enable/select access     | t <sub>EHQV</sub> | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            |            | 25          | ns   |

| time <u>4</u> /               | tslqv             | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                |            | <u>2</u> /  |      |

| Output hold after address     | t <sub>AVQX</sub> | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            | 3          |             | ns   |

| change                        |                   | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                | <u>2</u> / |             |      |

| Output enable access time     | t <sub>GLQV</sub> | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            |            | 9           | ns   |

|                               |                   | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                |            | <u>2</u> /  |      |

| Chip enable/select to         | t <sub>EHQX</sub> | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            | 5          |             | ns   |

| output active <u>4</u> /      | tslqx             | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                | <u>2</u> / |             |      |

| Output enable to output       | t <sub>GLQX</sub> | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            | 0          |             | ns   |

| active                        |                   | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                | <u>2</u> / |             |      |

| Chip disable/deselect to      | teLQZ             | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            |            | 10          | ns   |

| output disable <u>4</u> /     | tshqz             | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                |            | <u>2</u> /  |      |

| Output enable to output       | t <sub>GHQZ</sub> | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            |            | 9           | ns   |

| disable                       |                   | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                |            | <u>2</u> /  |      |

| Write enable to output        | twLQZ             | See figures 4 and 5                                                                                                                | 9, 10, 11            | All            |            | 9           | ns   |

| disable                       |                   | M, D, L, P, R, F, G, H                                                                                                             | 9 <u>1</u> /         |                |            | <u>2</u> /  |      |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 7    |

TABLE IA. Electrical performance characteristics - Continued.

| Test                         | Symbol            |                            | Group A subgroups | Device<br>type | Li                    | imits | Unit |

|------------------------------|-------------------|----------------------------|-------------------|----------------|-----------------------|-------|------|

|                              |                   | unless otherwise specified |                   |                | Min                   | Max   |      |

| Data setup to end of write   | t <sub>DVWH</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 15                    |       | ns   |

|                              |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Data hold after end of write | t <sub>WHDX</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 0                     |       | ns   |

|                              |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Output active after end of   | t <sub>WHQX</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 5                     |       | ns   |

| write                        |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Write cycle time 6/ 7/       | t <sub>AVAV</sub> | See figures 4 and 5        | 9, 10, 11         | 01 – 04        | 25                    |       | ns   |

|                              |                   |                            |                   | 05, 06         | 20                    |       |      |

|                              |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Chip enable/select to end    | t <sub>ЕНWН</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 20                    |       | ns   |

| of write <u>4</u> /          | tslwh             | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Address setup to end of      | t <sub>AVWH</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 20                    |       | ns   |

| write                        |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Address setup to start of    | t <sub>AVWL</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 0                     |       | ns   |

| write                        |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Write pulse width            | t <sub>WLWH</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 20                    |       | ns   |

|                              |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Address hold after end of    | t <sub>WHAX</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 0                     |       | ns   |

| write                        |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> /            |       |      |

| Write disable pulse width    | t <sub>WHWL</sub> | See figures 4 and 5        | 9, 10, 11         | All            | 5                     |       | ns   |

| <u>5</u> /                   |                   | M, D, L, P, R, F, G, H     | 9 <u>1</u> /      |                | <u>2</u> / <u>4</u> / |       |      |

<sup>1/</sup> When performing postirradiation electrical measurements for any RHA level  $T_A = +25^{\circ}C$ . Limits shown are guaranteed at  $T_A = +25^{\circ}C \pm 5^{\circ}C$ . The M, D, L, P, R, F, G, and H in the test condition column are the postirradiation limits for the device types specified in the device types column.

- 2/ Preirradiation values for RHA marked devices shall also be the postirradiation values, unless otherwise specified.

- $\overline{3}$ / f<sub>MAX</sub> = 1/t<sub>AVAV</sub> (minimum read cycle time).

- 4/ Input E and timing parameters tehov, tehox, teloz, and tehwh do not apply to devices in case outline X or Y.

- 5/ Tested initially and after any design or process changes which may affect that parameter, and therefore shall be guaranteed to the limits specified in table IA.

- 6/ Outputs disabled.

- 7/  $t_{AVAV} = t_{WLWH} + t_{WHWL}$ .

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 8    |

# TABLE IB. SEP test limits. 1/2/

| Device<br>type | lon type  | Memory<br>pattern | V <sub>CC</sub> = 4.5 V  SEU Rate Adam's 90% worst-case environment <u>3</u> / | Bias for latch-up test $V_{CC} = 5.5 \text{ V}$ , no latch-up LET = $\underline{4}$ / |

|----------------|-----------|-------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| All            | Heavy Ion | <u>5</u> /        | 1.0 x 10 <sup>-10</sup> upsets/bit-day                                         | LET ≤ 120 MeV-cm²/mg                                                                  |

- 1/ For SEP test conditions, see 4.4.4.3 herein.

- 2/ Technology characterization and model verification supplemented by in-line data may be used in lieu of end-of-line testing. Test plan must be approved by TRB and qualifying activity.

- 3/ Based on CREME96 results for a geosynchronous orbit during solar minimum non-flare conditions behind 100mil Aluminum shield. Weibull parameters are available from the vendor to calculate projected upset rates for other orbits/environments (such as Adams 90% worst case) and using different upset rate calculating programs (such as Space Radiation 5.0).

- $\underline{4}$ / Worst case temperature T<sub>A</sub> = +125°C ± 10°C for latch up.

- 5/ Testing shall be performed using checkerboard and checkerboard bar test patterns.

| STANDARD MICROCIRCUIT DRAWING DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 | SIZE<br><b>A</b> |                     | 5962-95845 |

|-------------------------------------------------------------------------------|------------------|---------------------|------------|

|                                                                               |                  | REVISION LEVEL<br>K | SHEET<br>9 |

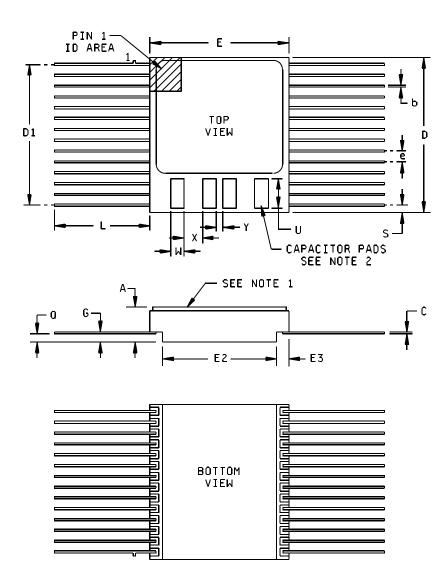

NOTE: The package may be assembled with CDR33 chip capacitors 0.1  $\mu$ F with 50V rating which meet approved criteria and are similar to MIL-PRF-123 capacitors.

FIGURE 1. <u>Case outlines</u> – Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 10   |

# Case Y - Continued.

| Symbol | Millimeters |       | Incl     | hes  |

|--------|-------------|-------|----------|------|

|        | Min         | Max   | Min      | Max  |

| Α      | 2.29        | 3.05  | .090     | .120 |

| b      | 0.38        | 0.48  | .015     | .019 |

| С      | 0.08        | 0.15  | .003     | .006 |

| D      | 18.08       | 18.49 | .712     | .728 |

| D1     | 16.38       | 16.64 | .645     | .655 |

| Е      | 12.52       | 12.88 | .493     | .507 |

| E2     | 9.45        | 9.86  | .372     | .388 |

| E3     | 1.52        | REF   | .060 BSC |      |

| е      | 1.27        | BSC   | .050 BSC |      |

| G      | 0.79        | 0.99  | .031     | .039 |

| L      | 7.49        |       | .295     |      |

| Q      | 0.66        | 1.14  | .026     | .045 |

| S      | 0.64        | 1.14  | .025     | .045 |

| U      | 3.30 REF    |       | .130 REF |      |

| W      | 1.27 REF    |       | .050     | REF  |

| Х      | 1.91        | REF   | .075 REF |      |

| Υ      | 0.25        | REF   | .010     | REF  |

# NOTES:

- 1. Lid tied to Vss.

- 2. The indicated terminal pad is P1. Terminal pads are numbered clockwise (top view) through P4.

FIGURE 1. <u>Case outlines</u> – Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95845 |

|----------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME            |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | K              | 11         |

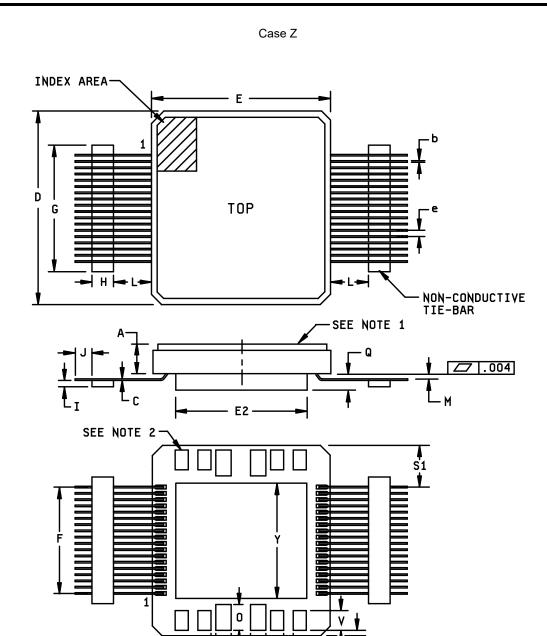

NOTE: The package may be assembled with CDR33 0.1  $\mu$ F and CDR32 .039  $\mu$ F chip capacitors with 50 V rating which meet approved criteria and are similar to MIL-PRF-123 capacitors.

FIGURE 1. Case outlines.

| STANDARD MICROCIRCUIT DRAWING                      | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 12   |

# Case Z - continued

| Symbol | Millim    | eters     | Incl     | hes   |

|--------|-----------|-----------|----------|-------|

|        | Min       | Max       | Min      | Max   |

| Α      | 2.16      | 2.67      | .085     | .105  |

| b      | 0.15      | 0.25      | .006     | .010  |

| С      | 0.127     | 0.191     | .0050    | .0075 |

| D      | 16.26     | 16.76     | .640     | .660  |

| Е      | 15.85     | 16.18     | .623     | .637  |

| E2     | 11.43     | REF       | .450     | REF   |

| е      | 0.635     | BSC       | .025     | BSC   |

| F      | 10.67     | 10.92     | .420     | .430  |

| G      | 13.34 REF |           | .525 REF |       |

| Н      | 3.43 REF  |           | .135 REF |       |

| I      | 0.64      | 0.64 0.89 |          | .035  |

| J      | 2.03      | REF       | .080 REF |       |

| L      | 6.86      | 7.62      | .270     | .300  |

| М      | 0.13      | 0.28      | .005     | .011  |

| 0      | 2.29      | REF       | .090 REF |       |

| Р      | 0.38      | REF       | .015 REF |       |

| Q      | 1.02      | 1.52      | .040     | .060  |

| R      | 1.91      | REF       | .075     | REF   |

| S1     | 2.62      | 3.12      | .103     | .123  |

| Т      | 1.27 REF  |           | .050     | REF   |

| U      | 0.76 REF  |           | .030     | REF   |

| V      | 2.03 REF  |           | .080     | REF   |

| W      | 0.13      | REF       | .005 REF |       |

| Υ      | 10.16     | REF       | .400     | REF   |

# NOTES:

- 1. Lid tied to Vss.

- 2. The indicated terminal pad is P1. Terminal pads are numbered clockwise (bottom view) through P12.

FIGURE 1. <u>Case outlines</u> - continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95845 |

|----------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME            |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | K              | 13         |

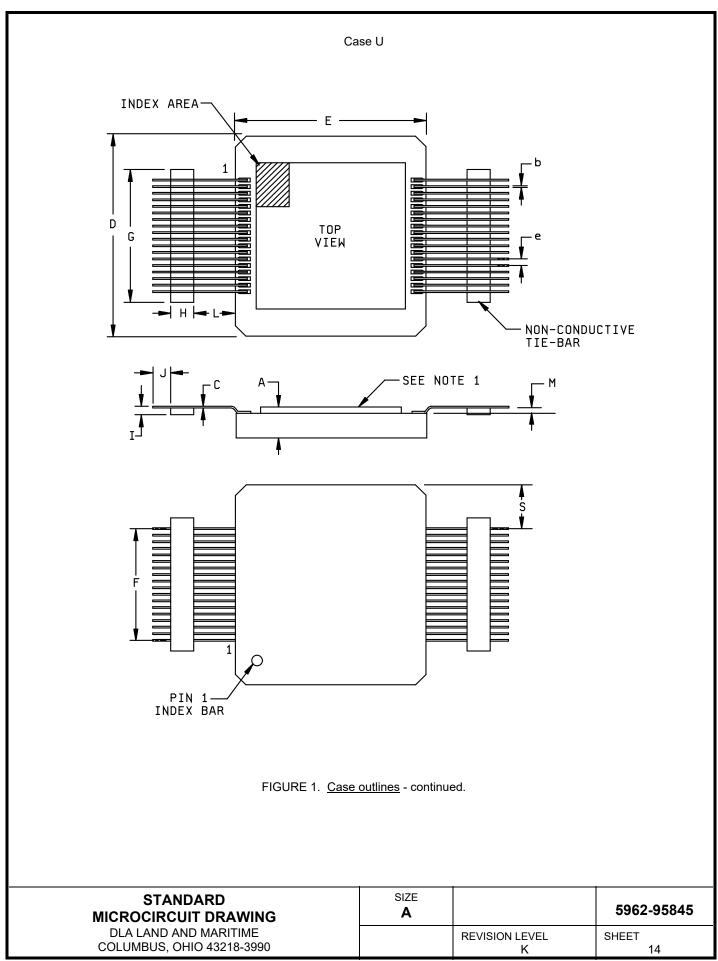

# Case U - Continued.

| Symbol          | Millim   | neters   | Inc      | hes   |

|-----------------|----------|----------|----------|-------|

|                 | Min      | Max      | Min      | Max   |

| Α               | 1.91     | 2.41     | .075     | .095  |

| b               | 0.15     | 0.25     | .006     | .010  |

| С               | 0.127    | 0.191    | .0050    | .0075 |

| D               | 16.26    | 16.76    | .640     | .660  |

| Е               | 15.85    | 16.18    | .623     | .637  |

| e<br>See note 2 | 0.635    | BSC      | .025     | BSC   |

| F<br>See note 2 | 10.67    | 10.92    | .420     | .430  |

| G               | 13.34    | REF      | .525 REF |       |

| Н               | 3.43 REF |          | .135     | REF   |

| I               | 0.64     | 0.89     | .025     | .035  |

| J               | 2.03     | 2.03 REF |          | REF   |

| L               | 6.86     | 7.37     | .270     | .290  |

| М               | 0.15     | 0.30     | .006     | .012  |

| S               | 2.62     | 3.12     | .103     | .123  |

# NOTES:

- 1. Lid tied to  $V_{\mbox{\footnotesize SS}}.$

- 2. Dimensions e and F are measured at the tie bar.

FIGURE 1. <u>Case outlines</u> – Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95845 |

|----------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME            |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | K              | 15         |

| Device type                                                                                                                                     | All                                                                                                                                                                                                                                                                                                                                   |                                                                                            |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Case outline                                                                                                                                    | Х                                                                                                                                                                                                                                                                                                                                     | Y                                                                                          | Z                                                                                                     | U                                                                                                                                                                                                                                                                                                                                                                              |

| Terminal no.                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                       | Termina                                                                                    | al symbol                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24             | A <sub>14</sub> A <sub>12</sub> A <sub>7</sub> A <sub>6</sub> A <sub>5</sub> A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> I/O <sub>0</sub> I/O <sub>2</sub> GND I/O <sub>3</sub> I/O <sub>4</sub> I/O <sub>5</sub> I/O <sub>6</sub> I/O <sub>7</sub> S A <sub>10</sub> G A <sub>11</sub> A <sub>9</sub> | A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 I/O0 I/O1 I/O2 GND I/O3 I/O4 I/O5 I/O6 I/O7 S A10 G A11 A9 | GND Vcc A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 I/O0 I/O1 I/O2 NC Vcc GND GND Vcc I/O3 I/O4 I/O5 I/O6         | GND<br>Vcc<br>A <sub>14</sub><br>A <sub>12</sub><br>A <sub>7</sub><br>A <sub>6</sub><br>A <sub>5</sub><br>A <sub>4</sub><br>A <sub>3</sub><br>A <sub>2</sub><br>A <sub>1</sub><br>A <sub>0</sub><br>I/O <sub>0</sub><br>I/O <sub>1</sub><br>I/O <sub>2</sub><br>NC<br>Vcc<br>GND<br>GND<br>Vcc<br>I/O <sub>3</sub><br>I/O <sub>4</sub><br>I/O <sub>5</sub><br>I/O <sub>6</sub> |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>P1<br>P2<br>P3<br>P4<br>P5<br>P6<br>P7<br>P8<br>P9<br>P10<br>P11<br>P12 | A8 A13 W Vcc                                                                                                                                                                                                                                                                                                                          | A8 A13 W Voc Voc GND Voc GND                                                               | I/O7 S A10 G A11 A9 A8 A13 EW VCC GND | I/O7 S A10 G A11 A9 A8 A13 E W VCC GND                                                                                                                                                                                                                                                                                                                                         |

FIGURE 2. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95845 |

|----------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME            |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | K              | 16         |

| Mode                 |                | Inputs (see notes 1 and 2) |            |            |          | Power   |

|----------------------|----------------|----------------------------|------------|------------|----------|---------|

|                      | E (see note 3) | S                          | W          | G          | I/O      |         |

| Write                | High           | Low                        | Low        | Don't care | Data in  | Active  |

| Read                 | High           | Low                        | High       | Low        | Data out | Active  |

| Standby              | Don't care     | High                       | Don't care | Don't care | High Z   | Standby |

| Read Standby         | High           | Low                        | High       | High       | High Z   | Standby |

| Standby (see note 4) | Low            | Don't care                 | Don't care | Don't care | High Z   | Standby |

#### NOTES:

- V<sub>IN</sub> for Don't Care inputs = V<sub>IL</sub> or V<sub>IH</sub>.

When G = high, I/O is High-Z.

Input E does not apply to devices in case outline X or Y.

When in standby mode, S = V<sub>CC</sub> and E = GND input levels to dissipate minimum standby power. All other input levels may float.

FIGURE 3. Truth table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95845 |

|----------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME            |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | K              | 17         |

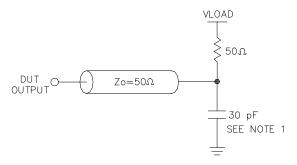

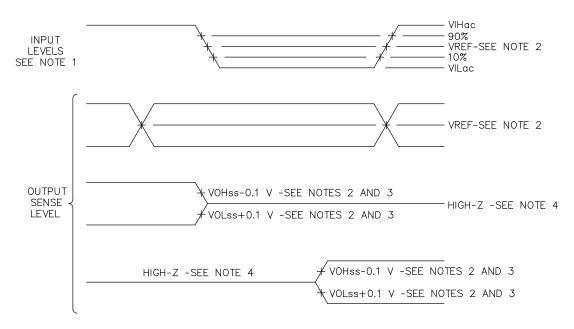

# AC Timing Output Load Circuit

NOTE 1: Set to 5 pF for T\*QZ (Low-Z to High-Z) timing parameters.

- 1. All input rise and fall times = 1 ns between the 90% and 10% levels

- 2. Timing parameter reference voltage level.

- 3. ss: Low-Z V<sub>OH</sub> and V<sub>OL</sub> steady state output voltage.

- 4. ss: High-Z output pin pulled to V<sub>Load</sub> by output load circuit.

| I/O type   | V <sub>ін</sub> ас | V <sub>IL</sub> ac      | $V_{REF}$            | $V_{LOAD}$           |

|------------|--------------------|-------------------------|----------------------|----------------------|

| 5.0 V CMOS | $V_{DDIO} - 0.5 V$ | V <sub>SS</sub> + 0.5 V | V <sub>DDIO</sub> /2 | V <sub>DDIO</sub> /2 |

| 5.0 V TTL  | 3.0 V              | 0.0 V                   | 1.5 V                | 1.5 V                |

FIGURE 4. Output load circuit.

| STANDARD MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95845 |

|-------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME         |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990     |                  | K              | 18         |

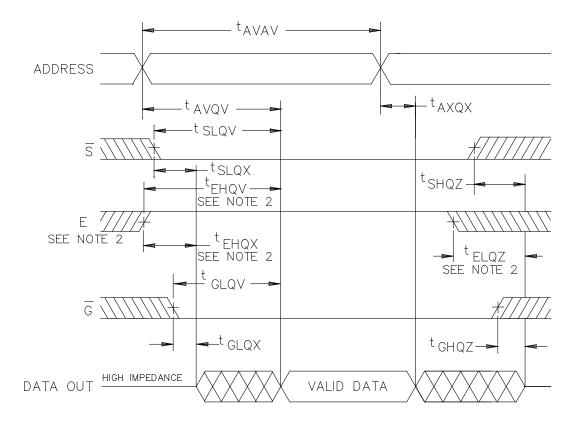

# Read cycle (see note 1)

- NOTES:

1. W is high for read cycle.

2. Input E and timing parameters t<sub>EHQV</sub>, t<sub>EHQX</sub>, and t<sub>ELQZ</sub> do not apply to devices in case outline X or Y.

FIGURE 5. Timing waveforms.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95845 |

|----------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME            |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | K              | 19         |

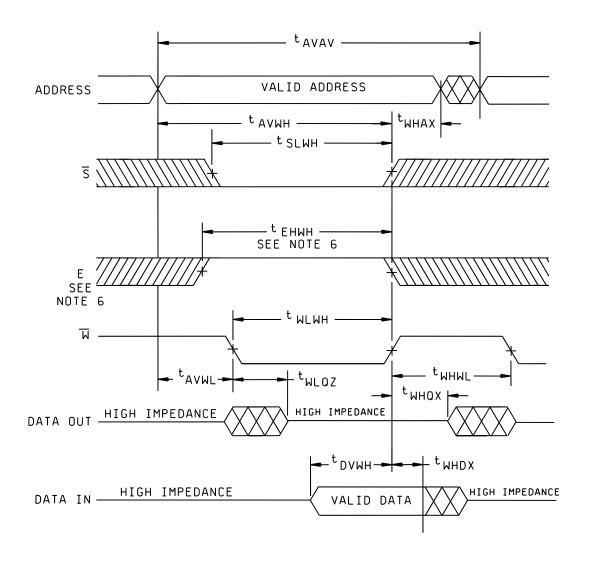

Write cycle (see notes 1, 2, 3, 4, and 5)

### NOTES:

- 1. Write cycle data is latched by the first occurrence of  $\overline{S}$  high, E low or  $\overline{W}$  high.

- 2.  $\overline{S}$  high,  $\overline{E}$  low, or  $\overline{W}$  high must occur while address transitions.

- 3. Write cycle time is guaranteed for toggling  $\overline{S}$  and E or holding  $\overline{S}$  or E, or both, in active state.

- 4. The worst case timing sequence of twLQZ + tDVWH + twHWL = the write cycle time (tAVAV).

- 5.  $\overline{G}$  high will eliminate the I/O output from becoming active ( $t_{WLQZ}$ ).

- 6. Input E and timing parameter tehwh do not apply to devices in case outline X or Y.

FIGURE 5. <u>Timing waveforms</u> – Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 20   |

TABLE IIA. Electrical test requirements. 1/ 2/ 3/ 4/ 5/ 6/

| Line<br>no. | Test requirements                                 | Subgroups<br>(in accordance with<br>MIL-PRF-38535, table III) |                                       |

|-------------|---------------------------------------------------|---------------------------------------------------------------|---------------------------------------|

|             |                                                   | Device<br>class Q                                             | Device<br>class V                     |

| 1           | Interim electrical parameters (see 4.2)           |                                                               | 1, 7, 9                               |

| 2           | Static burn-in I and II<br>(method 1015)          | Not<br>required                                               | Required                              |

| 3           | Same as line 1                                    |                                                               | 1*, 7* Δ                              |

| 4           | Dynamic burn-in (method<br>1015)                  | Required                                                      | Required                              |

| 5           | Same as line 1                                    |                                                               | 1*, 7* Δ                              |

| 6           | Final electrical parameters (see 4.2)             | 1*, 2, 3, 7*,<br>8A, 8B, 9, 10, 11                            | 1*, 2, 3, 7*,<br>8A, 8B, 9, 10, 11    |

| 7           | Group A test requirements (see 4.4)               | 1, 2, 3, 4**, 7,<br>8A, 8B, 9, 10, 11                         | 1, 2, 3, 4**, 7,<br>8A, 8B, 9, 10, 11 |

| 8           | Group C end-point electrical parameters (see 4.4) | 1, 2, 3, 7, 8A, 8B                                            | 1, 2, 3, 7, 8A,<br>8B, 9, 10, 11 Δ    |

| 9           | Group D end-point electrical parameters (see 4.4) | 1, 7, 9                                                       | 1, 7, 9                               |

| 10          | Group E end-point electrical parameters (see 4.4) | 1, 7, 9                                                       | 1, 7, 9                               |

- 1/ Blank spaces indicate tests are not applicable.

- 2/ Any or all subgroups may be combined when using high-speed testers.

- 3/ Subgroups 7, 8A, and 8B functional tests shall verify the truth table.

- 4/ \* indicates PDA applies to subgroup 1 and 7.

- $\frac{-}{5}$ / \*\* see 4.4.1d.

- 6/ \( \Delta \) indicates delta limit (see table IIB) shall be required where specified, and the delta values shall be computed with reference to the previous interim electrical parameters (see line 1). For device class V performance of delta limits shall be as specified in the manufacturer's QM plan.

TABLE IIB. Delta limits at +25°C.

| Test <u>1</u> /          | Device types                        |  |

|--------------------------|-------------------------------------|--|

|                          | All                                 |  |

| I <sub>CC3</sub> standby | ±10% of specified value in table IA |  |

| IILK, IOLK               | ±10% of specified value in table IA |  |

1/ The above parameters shall be recorded before and after the required burn-in and life tests to determine the delta.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 21   |

#### 4. VERIFICATION

- 4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

- 4.3 <u>Qualification inspection for device classes Q and V.</u> Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

- 4.4 <u>Conformance inspection</u>. Technology conformance inspection for classes Q and V shall be in accordance with MIL-PRF-38535 including groups A, B, C, D, and E inspections and as specified herein.

- 4.4.1 Group A inspection.

- a. Tests shall be as specified in table IIA herein.

- b. Subgroups 5 and 6 of table I of method 5005 of MIL-STD-883 shall be omitted.

- c. For device classes Q and V, subgroups 7, 8A, and 8B shall include verifying the functionality of the device; these tests shall have been fault graded in accordance with MIL-STD-883, method 5012 (see 1.5 herein).

- d. O/V (Latch-up) tests shall be measured only for the initial qualification and after any process or design changes which may affect the performance of the device. For device classes Q and V, the procedures and circuit shall be under the control of the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the preparing or acquiring activity upon request. Testing shall be on all pins, on five devices with zero failures. Latch-up test shall be considered destructive. Information contained in JESD 78 may be used for reference.

- e. Subgroup 4 (C<sub>IN</sub> and C<sub>OUT</sub> measurements) shall be measured only for initial qualification and after any process or design changes which may affect input or output capacitance. Capacitance shall be measured between the designated terminal and GND at a frequency of 1 MHz. Sample size is 15 devices with no failures, and all input and output terminals tested.

- 4.4.2 Group C inspection. The group C inspection end-point electrical parameters shall be as specified in table IIA herein.

- 4.4.2.1 <u>Additional criteria for device classes Q and V</u>. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

- 4.4.3 Group D inspection. The group D inspection end-point electrical parameters shall be as specified in table IIA herein.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 22   |

- 4.4.4 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein).

- a. End-point electrical parameters shall be as specified in table IIA herein.

- b. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535 for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table IA at  $T_A = +25$ °C, after exposure, to the subgroups specified in table IIA herein.

- c. For device classes Q and V subgroups 1 and 2 of table C-I or table B-I (appendix B) of MIL-PRF-38535, shall be tested as appropriate for device construction.

- 4.4.4.1 <u>Total dose irradiation testing</u>. Total dose irradiation testing shall be performed in accordance with MIL-STD-883 method 1019, condition A, and as specified herein. The total dose requirements shall be as defined within paragraph 1.5 herein.

- 4.4.4.1.1 <u>Accelerated annealing test</u>. Accelerated annealing tests shall be performed on all devices requiring a RHA level greater than 5 krad(Si). The post-anneal end-point electrical parameter limits shall be as specified in Table IA herein and shall be the pre-irradiation end-point electrical parameter limit at 25°C ±5°C. Testing shall be performed at initial qualification and after any design or process changes which may affect the RHA response of the device.

#### 4.4.4.2 Transient dose rate upset.

- a. For device types 01, 02, 05, and 06, devices shall be capable of retaining stored data during and after exposure to a transient ionizing radiation pulse of ≤ 20 ns up to and including 10<sup>9</sup> Rads (Si)/sec when applied under recommended operating conditions.

- b. For device types 03 and 04, devices shall be capable of retaining stored data during and after exposure to a transient ionizing radiation pulse of ≤ 20 ns up to and including 10<sup>9</sup> Rads (Si)/sec when applied under recommended operating conditions.

- c. The dose rate upset specification is valid only if the V<sub>DD</sub> to V<sub>SS</sub> potential difference applied to the package remains within the recommended operation range during transient radiation.

- d. Transient dose rate survivability Device types 01, 02, 05, 06 shall not be rendered permanently incapable of meeting any functional or electrical specification by a ≤ 20 ns transient ionizing radiation pulse of up to and including 10<sup>11</sup> Rads (Si)/sec when applied under recommended operating conditions.

The current conducted during the pulse in the SRAM inputs, outputs, and particularly power supply may significantly exceed the normal operating levels.

- e. Transient dose rate survivability Device types 03 and 04 shall not be rendered permanently incapable of meeting any functional or electrical specification by a ≤ 20 ns transient ionizing radiation pulse of up to and including 10<sup>12</sup> Rads (Si)/sec when applied under recommended operating conditions.

The current conducted during the pulse in the SRAM inputs, outputs, and particularly power supply may significantly

- The current conducted during the pulse in the SRAM inputs, outputs, and particularly power supply may significantly exceed the normal operating levels.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-95845 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>K | SHEET 23   |

- 4.4.4.3 <u>Single event phenomena (SEP)</u>. SEP testing shall be required on class V devices. SEP testing shall be performed on the SEC or alternate SEP test vehicle as approved by the qualifying activity at initial qualification and after any design or process changes which may affect the upset or latch-up characteristics. Test four devices with zero failures. ASTM standard F1192 may be used as a guideline when performing SEP testing. The test conditions for SEP are as follows:

- a. The ion beam angle of incidence shall be normal to the die surface and 60 degrees to the normal, inclusive (i.e.,  $0^{\circ} \le$  angle  $\le 60^{\circ}$ ). No shadowing of the ion beam due to fixturing or package related effects is allowed.